1. Tujuan [back]

Untuk mengukur pemahaman mahasiswa, diharapkan mahasiswa membuat rangkaian aplikasi dari

materi yang dipahami

Resistor

Resistor atau hambatan adalah salah satu komponen

elektronika yang memiliki nilai hambatan tertentu, dimana hambatan ini akan

menghambat arus listrik yang mengalir melaluinya. Sebuah resistor biasanya

terbuat dari bahan campuran Carbon. Namun tidak sedikit juga resistor yang

terbuat dari kawat nikrom, sebuah kawat yang memiliki resistansi yang cukup

tinggi dan tahan pada arus kuat. Contoh lain penggunaan kawat nikrom dapat

dilihat pada elemen pemanas setrika. Jika elemen pemanas tersebut dibuka, maka

terdapat seutas kawat spiral yang biasa disebut dengan kawat nikrom

LDR

DR (Light Dependent Resistor) merupakan salah satu komponen

resistor yang nilai resistansinya akan berubah-ubah sesuai dengan intensitas

cahaya yang mengenai sensor ini. LDR juga dapat digunakan sebagai sensor

cahaya. Perlu diketahui bahwa nilai resistansi dari sensor ini sangat

bergantung pada intensitas cahaya. Semakin banyak cahaya yang mengenainya, maka

akan semakin menurun nilai resistansinya. Sebaliknya jika semakin sedikit

cahaya yang mengenai sensor (gelap), maka nilai hambatannya akan menjadi

semakin besar sehingga arus listrik yang mengalir akan terhambat.

Prinsip kerja LDR sangat sederhana tak jauh berbeda dengan

variable resistor pada umumnya. LDR dipasang pada berbagai macam rangkaian

elektronika dan dapat memutus dan menyambungkan aliran listrik berdasarkan

cahaya. Semakin banyak cahaya yang mengenai LDR maka nilai resistansinya akan

menurun, dan sebaliknya semakin sedikit cahaya yang mengenai LDR maka nilai

hambatannya akan semakin membesar.

Gerbang NOT

Gerbang NOT hanya memerlukan sebuah Masukan (Input)

untuk menghasilkan hanya 1 Keluaran (Output). Gerbang NOT disebut juga dengan

Inverter (Pembalik) karena menghasilkan Keluaran (Output) yang berlawanan

(kebalikan) dengan Masukan atau Inputnya. Berarti jika kita ingin mendapatkan

Keluaran (Output) dengan nilai Logika 0 maka Input atau Masukannya harus

bernilai Logika 1. Gerbang NOT biasanya dilambangkan dengan simbol minus (“-“)

di atas Variabel Inputnya.

LM358

LM358 IC adalah kekuatan besar, rendah serta gampang

dipakai dual channel op-amp IC. Ini dirancang serta diperkenalkan oleh

semikonduktor nasional. Ini terdiri dari dua kompensasi internal, gain tinggi,

op-amp independen. IC ini dirancang untuk khusus beroperasi dari catu daya

tunggal melewati beberapa tegangan. IC LM358 terdapat dalam paket berkapasitas chip

serta software op amp ini tergolong rangkaian op-amp konvensional, blok

penguatan DC, serta amplifier transduser. LM358 IC adalah penguat operasional

standar yang bagus serta amatlah tepat untuk kebutuhan Anda. Bisa menangani

pasokan & sumber DC 3-32V sampai 20mA per saluran. Op-amp ini amatlah

tepat, apabila Kamu ingin mengoperasikan dua op-amp terpisah untuk catu daya

tunggal. Ini terdapat dalam paket DIP 8-pin.

Pin-1 dan pin-8 adalah o / p dari

komparator

Pin-2 dan pin-6 adalah pembalik i

/ id

Pin-3 dan pin-5 adalah non

inverting i / id

Pin-4 adalah terminal GND

Pin-8 adalah VCC +

LM358 IC Pin Configuration

LM358 IC Pin Configuration

Fitur LM358 IC

Fitur dari LM358 IC adalah

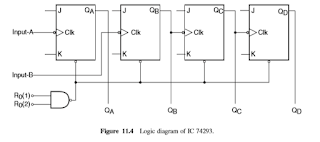

IC 74192

IC 74192 adalah sebuah ic counter up dan juga bisa digunakan sebagai counter down yang output nya berupa data BCD (binary coded decimal) yaitu 4 buah output yang mewakili bilangan biner. Bila input clock dari IC counter ini diberikan satu buah siklus clock (high dan low) maka nilai output BCD nya akan berubah tergantung dari dimana clock tersebut diberikan, apakah pada bagian clock up atau ada clock down. Pin clock input terletak pada kaki IC 4 dan 5 dimana kaki nomor 4 adalah clock input untuk count down sedangkan kaki nomor 5 digunakan untuk count up. Output yang berupa data BCD ini tentunya akan sangat sulit untuk dipahami bagi orang awam, karena harus mentranslatekan bilangan biner tersebut ke bilangan decimal terlebih dahulu. Maka dari itu kita menggunakan bantuan dari sebuah IC yang mampu mengatasi masalah konversi bilangan biner ke decimal secara langsung.

IC 74247

IC Dekoder BCD ke 7

Segmen 74LS247 berfungsi untuk mengubah data input yang berupa

sandi Binary Coded Decimal (BCD) menjadi sandi yang sesuai dengan format

7 segmen. Dekoder BCD ke 7 segmen IC 74LS247 ini digunakan

untuk mengubah data bcd 4 bit dari mikrokontroleratau perangkat digital lain

menjadi sinyal atau logika yang bisa digunakan untuk menyalakan penampil 7

segmen sesuai nilai dari data BCD inputnya. IC Dekoder 74LS247 mempunyai

4 buah data masukan, masing-masing A, B, C, dan D tujuh buah keluaran yaitu :

a, b, c, d, e, f dan beberapa kaki untuk kendali yaitu , RB In (RBI), RB

Out (RBO). Untuk mengoperasikan “IC dekoder 74LS247” agar keluaran a – g

menghasilkan tampilan desimal dari data BCD pada masukan A0 – A3 maka

kaki dan BI diberi logika tinggi kemudian data BCD diberikan pada

kaki-kaki A0 – A3. Fasilitas (Lamp Test digunakan untuk mengetes kondisi

penampil 7 segmen. Fasilitas BI (Blanking Input) berfunsi untuk

meniadakan data masukan dan memberikan tampilan blank pada penampil 7 segmen.

Output dekoder IC 74LS247 pada jalur a – f dihubungkan ke jalur input

penampil 7 segmen.

Fungsi Kaki IC Dekoder BCD Ke 7 Segmen 74LS247 Adalah Sebagai Berikut:

1. Kaki A0 – A3 berfungsi sebagai jalur masukan data BCD 4 bit.

2. Kaki RBI berfungsi sebagai masukan kontrol Riple Blanking Input.

3. Kaki berfungsi sebagai masukan kontrol Lamp Test.

4. Kaki BI/ berfungsi sebagai masukan kontrol Blanking Input atau Riple Blanking Output.

5. Kaki a – g berfungsi sebagai keluaran untuk penampil 7 segmen common anode.

2. Kaki RBI berfungsi sebagai masukan kontrol Riple Blanking Input.

3. Kaki berfungsi sebagai masukan kontrol Lamp Test.

4. Kaki BI/ berfungsi sebagai masukan kontrol Blanking Input atau Riple Blanking Output.

5. Kaki a – g berfungsi sebagai keluaran untuk penampil 7 segmen common anode.

IC Dekoder BCD ke 7 Segmen 74LS247 dioperasikan dengan sumber tegangan DC +5 volt sama seperti IC TTL

.

Seven Segment

Seven Segment Display (7 Segment

Display) dalam bahasa Indonesia disebut dengan Layar Tujuh Segmen adalah

komponen Elektronika yang dapat menampilkan angka desimal melalui

kombinasi-kombinasi segmennya. Seven Segment Display pada umumnya dipakai pada

Jam Digital, Kalkulator, Penghitung atau Counter Digital, Multimeter Digital

dan juga Panel Display Digital seperti pada Microwave Oven ataupun Pengatur

Suhu Digital . Seven Segment Display pertama diperkenalkan dan dipatenkan pada

tahun 1908 oleh Frank. W. Wood dan mulai dikenal luas pada tahun 1970-an

setelah aplikasinya pada LED (Light Emitting Diode).

Seven Segment Display memiliki 7

Segmen dimana setiap segmen dikendalikan secara ON dan OFF untuk menampilkan angka

yang diinginkan. Angka-angka dari 0 (nol) sampai 9 (Sembilan) dapat ditampilkan

dengan menggunakan beberapa kombinasi Segmen. Selain 0 – 9, Seven Segment

Display juga dapat menampilkan Huruf Hexadecimal dari A sampai F. Segmen atau

elemen-elemen pada Seven Segment Display diatur menjadi bentuk angka “8” yang

agak miring ke kanan dengan tujuan untuk mempermudah pembacaannya. Pada

beberapa jenis Seven Segment Display, terdapat juga penambahan “titik” yang

menunjukan angka koma decimal. Terdapat

beberapa jenis Seven Segment Display, diantaranya adalah Incandescent bulbs,

Fluorescent lamps (FL), Liquid Crystal Display (LCD) dan Light Emitting Diode

(LED).

Pada LED 7 Segmen jenis Common

Cathode (Katoda), Kaki Katoda pada semua segmen LED adalah terhubung menjadi 1

Pin, sedangkan Kaki Anoda akan menjadi Input untuk masing-masing Segmen

LED. Kaki Katoda yang terhubung menjadi 1 Pin ini merupakan Terminal

Negatif (-) atau Ground sedangkan Signal Kendali (Control Signal) akan

diberikan kepada masing-masing Kaki Anoda Segmen LED.

Prinsip kerja :

Pada rangkaian diatas LDR berfungsi sebagai detektor ketika ada sebuah kendaraan memasukui tempat parkir. Ketika sebuah kendaraan masuk, akan ada cahaya yang mengenai sensor kemudian menjauh, ketika hal ini terjadi maka akan ada tengan yang keluar dari LDR menuju LM538N. Tegangan dari sumber juga akan melalui R1 dan juga ke resistor variabel kemudian masuk ke kaki lm538. Kemudia diteruskan menuju inverter, disini terdapat LED yang menjadi indikator ketika cahaya dari kendaraan mendekati sensor dan ketika cahaya dari kendaraan menjauhi sensor. Kemudia di teruskan ke ic 74ls192 yang berfungsi sebagai up and down decoder counter. Tegangan ini akan masuk ke kami up dari IC kemudian ic74ls247 akan menerjemahkannya menjadi bentuk desimal, menjadi counter up. Begitupun ketika kendaraan menjauhi tempat parkir, tegangan yang dihasilkan akan masuk melalui kaki down ic 74ls192 kemudia diterjemahkan ic 74ls247 menjadi bilangan desimal, counter down.

HTML : download

Rangkaian : download

Video : download

Datasheet IC74248 :Download

Datasheet IC74192 :Download

Datasheet 7-segmen:Download

Datasheet LM358 : Download

Datasheet IC74248 :Download

Datasheet IC74192 :Download

Datasheet 7-segmen:Download

Datasheet LM358 : Download

.